# Merged PiN and Schottky (MPS) Power Diodes Electrothermal Modeling in SPICE

Abderrazak LAKRIM, Student Member IEEE, Driss TAHRI

Signals, Systems and Components Laboratory (SSCL), EMC and Power Electronic Systems, Team, Faculty of Science and Technology of Fez, BP.2202

\* E-mail of the corresponding author: abderrazak.lakrim@usmba.ac.ma

#### **Abstract**

This paper sets out a behavioral macro-model of a Merged PiN and Schottky (MPS) diode based on silicon carbide (SiC). This model holds good for both static and dynamic electro-thermal simulations for industrial applications. Its parameters have been worked out from datasheets curves by drawing on the optimization method: Simulated Annealing (SA) for the SiC MPS diodes made available in the industry. The model also adopts the Analog Behavioral Model (ABM) of PSPICE in which it has been implemented. The thermal behavior of the devices was also taken into consideration by making use of Foster' canonical network as figured out from electro-thermal measurement provided by the manufacturer of the device.

Keywords: SiC MPS Diode, Electro-thermal, SPICE Model.

#### 1. Introduction

The silicon carbide power devices are the most promising semiconductor devices for industrial power applications, for they are characterized by a high heat resistance, excellent thermal properties and effective performance at high switching frequencies and power levels. Nowadays, the MPS diodes are the most widely used, and provide a better adjustment between the forward voltage drops and reverse bias leakage current, following a voltage drop at the junction level [1] [2].

Nevertheless; untill now no excellent model has been conjured up, which will be qualified to predict the characteristics of the semiconductor device in a relatively wide-ranging operating temperature. Moreover; the accurate forecasting of the device behavior is still necessarily entailed for a vigorous supply design and for predicting electromagnetic interferences (EMI). And while there are classical models of SPICE based on physics of semiconductor [3] [4] [5] [6], and others provided by manufacturers, none of them, however, can produce precise characteristics of a temperature-dependent device.

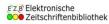

#### 2. Behavioral Macro Model of MPS Diodes in Spice

Although several macro-model of MPS diode power have been proposed in Spice [7] [8] [9], they are, however, rather complex in the extraction of their parameters, unlike the proposed model which is quite simple, flexible and very much practical for all types of semiconductor. This model is made up of two parts; one electrical consisting, in the static state, of forward voltage drop and reverse bias leakage current; and in the dynamic state, of the reverse bias charge; the other is thermal and takes the form of an RC Foster network [10] [11]. This model is represented in the figure 1.

# 2.1 The electrical part of the model

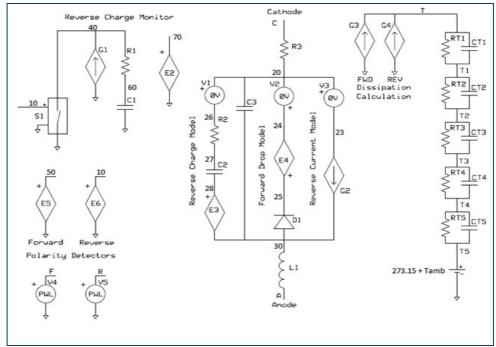

## 2.1.1 The forward voltage drop

On our part we propose a simpler way to modelize the characteristics of the diode's forward voltage drop by using the ABM blocks of the SPICE; i.e. by having recourse to a voltage controlled voltage source (VCVS) controlled by the appropriate equation. In order to clearly distinguish between forward and reverse bias conditions, the forward voltage drop model includes a "reference diode" series with the VSCV E4 and in which the parameters N and Temp are set to specific values, "N = 0.5" and "Temp=27°C" [12], [13], [14].

Figure 1: the Subcircuit Diagram proposed model

The parameters of the diode change in the course of the time, while the parameters of the reference diode retain their default values unchanged. The forward voltage drop of the reference diode, shown in Figure 2, has an approximately constant and low variation, depending on the current; whereas taking account of temperature is provided by the VCVS E4 in series with the reference diode.

Figure 2: Voltage drop contributions with current

The forward Voltage drop can be represented by the logarithmic component (equation 2) plus the reference diode's constant drop voltage component ID \* RS (equation 3) which is due to an RS resistance that represents the sum of both the diffusion substrate resistance and contact resistance [15].

$$I_D = I_S \left( \exp\left(\frac{q \cdot V_j}{K \cdot T}\right) + 1 \right) \tag{1}$$

$$V_{j} = \log\left(\frac{I_{D}}{I_{S}} + 1\right) \times \left(VF10 + VF11 \times V(T) + VF12 \times V(T)^{2}\right) \times 0.0257$$

(2)

$$V_C = I(V2) \times (VF20 + VF21 \times V(T) + VF22 \times V(T)^2) \times 0.0257$$

(3)

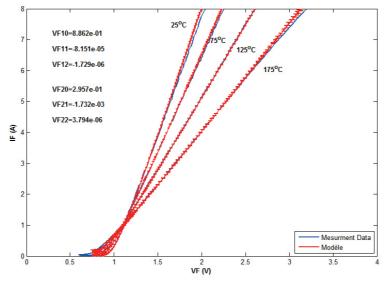

Here VF10, VF11, VF12, VF20, VF21, and VF22 (see Table I) are the coefficients of the interpolation polynomial of the curve (temperature-dependent forward voltage drop) provided by the manufacturer.

## 2.1.2 The leakage current in reverse

it is well known that modeling the reverse bias leakage current and breakdown voltage has evoked much attention in power electronic literature such as in Mantooth for example [16] where five reverse bias effects were added to the saturation current of the diode in Saber platform; while Maxim [17] proposed in turn a model based on the physics of semiconductor, with SPICE ABM blocks, including the reverse bias leakage current and avalanche effects.

The effects of leakage current and breakdown voltage may be either significant or otherwise in accordance with the voltage and power levels of the converter. In cases when one of these characteristics is insignificant, the model can be further simplified (by reducing complexity and the time of simulation).

However; If the leakage current vastly contributes to dissipation then it can be modeled by G2 which is an ABM source current controlled by an equation determined on the basis of the manufacturer's data. The control equation of the G2 is:

$$I_{R} = Eq1 \times \left(\frac{V(A)^{2}}{Eq2}\right)^{(Eq3)}$$

$$Eq1 = IR10 + IR11 \times V(T) + IR12 \times V(T)^{2}$$

$$Eq2 = IR20 + IR21 \times V(T) + IR22 \times V(T)^{2}$$

$$Eq3 = IR30 + IR31 \times V(T) + IR32 \times V(T)^{2}$$

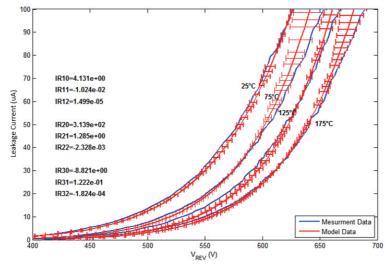

The above IR10, IR11, IR12, IR20, IR21, F22, IR30, IR31, and IR32 are the coefficients of the interpolation polynomial of the curve (reverse bias leakage current as a function of temperature) given by the manufacturer.

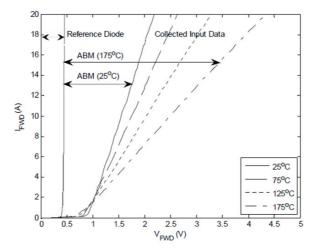

## 2.1.3 The reverse bias

The reverse recovery phenomenon takes place when a negative voltage is applied to the terminals of a conductive diode, yielding up the curves shown in Figure 3. The curve of the current is split into three phases [18]:

Figure 3: The tree phases of reverse recovery

**Phase 0:** ends when the diode begins to turn off.

**Phase 1**: is the charge storing stage during which excessive charges in the P region evacuated out. The charge control equation for minority carriers in the turn-off process is written as follows:

$$\frac{dQ(t)}{dt} + \frac{Q(t)}{\tau_E} = -i_n(0, t) = -i(t)$$

(5)

If we consider the current through the depletion capacity as well, equation (5) can be rewritten as follows:

$$\frac{dQ(t)}{dt} + \frac{Q(t)}{\tau_{r}} - \overline{C}_{jn} \frac{dV(t)}{dt} = -i(t)$$

(6)

**Phase 2:** During this phase, the control and variation of the charge are non-linear (see figure 3), and in this case, the latter is described by the equation (7) [17].

$$|Q(t)| = |i(t).\tau_R| \tag{7}$$

The current through Cjn cannot be overlooked since a junction voltage is about to be generated. So we use the equation (6) as a charge control equation.

By applying this reasoning to our model:

It follows that the turn-off of the diode starts when the switch S1 is turned on and results in the G1 current flow through the R1-C1 circuit (Fig 1).

The E2 source (VCVS) controlled by a voltage V(60) across C1, generates at its output a voltage V(70), which is the control voltage source E3 (VCVS). Initially, this voltage (V(70)) has a negative value which allows a linear storage of the charges in the capacitor C3 (equation 5). As soon as the voltage E3 (equation 8) becomes positive, reverse recovery phase (phase 2) starts and instigates removal of C3 charges through the R2 resistor. Once V (E3) reaches its maximum value, the capacitor C2 obtains the same potential across its terminals; Then the I(V1) current vanishes, cancels G1 input and sets its output current to 0 value, so that the output voltages of E2 and E3 sources automatically reaches zero (Fig 1).

$$V = V(70) \times (QR10 + QR11 \times V(70) + QR12 \times V(70)^{2})$$

(8)

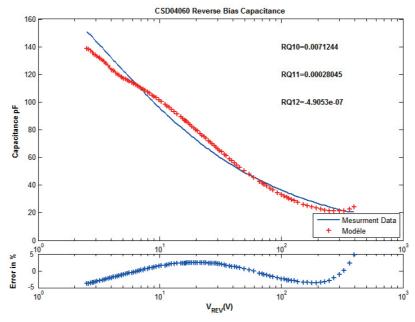

QR10, QR11, and QR12 are the coefficients of the interpolation polynomial of the curve (variation of the C capacitor as a function of Vrev reverse voltage) given by the manufacturer.

## 2.2 The thermal part model

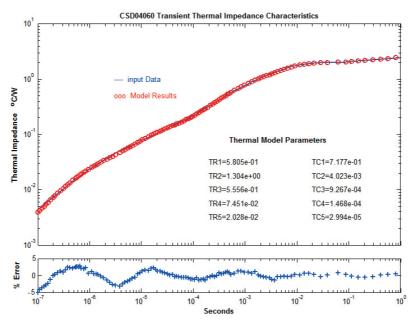

The thermal impedance provided by the manufacturer's datasheet represents the instantaneous increase in the

junction temperature of the device as a function of time [19]. It is represented by the RC pair of cells [20] [21] [22] [23], and is dependent on the size of the semiconductor, the number and type of layers between the semiconductor and its case, and also the electrical insulation material. For our model we used 5 cells RC parallel.

The values of Ri and Ci are derived from the datasheet curve [19], [25], [26], [27], [28], and calculated depending on Zth values (column Y) and τi (column X) for each n RC pairs according to equation (9).

$$Z_{Th}(t) = \sum_{i=1}^{n} R_i \left( 1 - \exp\left(\frac{-t}{\tau_i}\right) \right)$$

(9)

We first determine ZThmax maximum value (in permanent state), and then the approximate values of the first pole position which are defined by ZTh and its corresponding  $\tau$  (x-axis) (equation 10). The remained values of Rn and  $\tau$ n are respectively determined according to equations (11) and (12).

$$Z_{Th} = 0.7 \times Z_{Th \, \text{max}} \tag{10}$$

$$R_n = R_1 \times 0.5^n \tag{11}$$

$$\tau_n = \frac{\tau_1}{n} \left( 0.1^{n-1} \right) \tag{12}$$

We use the Simulated Annealing (SA) [24], technique to browse randomly (starting from an initialization) the pair values Zth and  $\tau$ . Then, we compare the error of the current iteration with the best error formerly found. The latter is calculated by the least squares (LS) method for each time step (i) (equation 13).

$$Erreur = \sum_{1}^{n} \left( \frac{R_{\theta}(i) - R_{\theta}(i)best}{R_{\theta}(i)best} \right)^{2}$$

(13)

#### 3. Results

To assess the accuracy of the proposed model described in II, we performed simulations of some SiC MPS Diodes models (C3D04060E [19], CSD04060 [25], CSD10030 [26], SDP04S60 [27], et SDP10S30 [28]), by using Orcad 16.6 Spice simulator. The values of model parameters obtained for all the tested devices are summarized in the below Table as follow.

The external environment is presented by a voltage source whose value is the ambient temperature (Fig 1). This model is valid for the 2nd and 3rd generation SiC MPS diodes.

The simulation results showed excellent correspondence to the measured curves provided by the manufacturer's datasheets for all voltages and currents in both forward and reverse bias, and in a wide range of operating temperature. An example of the obtained results for the simulations of CSD04060 diode in forward and reverse bias is shown respectively in Figures 4 and 5, and all the curves of these figures correspond to the 25°C, 75°C, 125°C and 150°C temperature values. The thermal impedance curve is shown in Figure 6 and the reverse recovery charge in Figure 7. All these curves are presented with error bars of 5%.

Table 1. The capitals, assets and revenue in listed banks

|                              |     | C3D04060E  | CSD04060     | CSD10030   | SDP04S60   | SDP10S30   |

|------------------------------|-----|------------|--------------|------------|------------|------------|

| Thermal Parameters           |     |            |              |            |            |            |

| TR                           | TR1 | 2.432e-01  | 5.654e-01    | 5.838e-01  | 3.459e-02  | 1.450e-01  |

|                              | TR2 | 9.938e-01  | 1.353e+00    | 4.679e-01  | 6.801e-01  | 3.305e-01  |

|                              | TR3 | 1.211e+00  | 4.806e-01    | 7.535e-01  | 2.115e+00  | 9.898e-01  |

|                              | TR4 | 2.675e-01  | 7.073e-02    | 7.535e-01  | 1.613e-01  | 1.067e-01  |

|                              | TR5 | 4.541e-02  | 1.874e-02    | 2.107e-02  | 3.287e-01  | 1.816e-01  |

| тс                           | TC1 | 4.363e-01  | 5.609e-01    | 2.484e-01  | 6.597e+01  | 5.359e-01  |

|                              | TC2 | 1.890e-02  | 3.401e-03    | 2.955e-02  | 3.550e-02  | 4.597e-02  |

|                              | TC3 | 1.674e-03  | 8.970e-04    | 2.058e-03  | 1.230e-03  | 4.028e-03  |

|                              | TC4 | 1.671e-03  | 1.341e-04    | 4.246e-04  | 2.679e-04  | 1.141e-03  |

|                              | TC5 | 1.337e-03  | 3.021e-05    | 4.309e-05  | 1.375e-08  | 2.031e-07  |

| Forward Voltage Drop         |     |            |              |            |            |            |

| VF10                         |     | 5.871e-01  | 8.862e-01    | 7.123e-01  | 8.659e-01  | 9.548e-01  |

| VF11                         |     | 9.642e-04  | -8.151e-05   | -1.721e-03 | 1.398e-04  | -8.042e-04 |

| VF12                         |     | -2.991e-06 | -1.729e-06   | 5.297e-07  | -2.238e-06 | -6.598e-07 |

| VF20                         |     | 2.885e-01  | 2.957e-01    | 9.332e-02  | 3.963e-01  | 1.001e-01  |

| VF21                         |     | -1.426e-03 | -1.732e-03   | -3.877e-04 | -1.967e-03 | -3.816e-04 |

| VF22                         |     | 2.847e-06  | 3.794e-06    | 8.559e-07  | 3.956e-06  | 6.596e-07  |

| Reverse Bias Charge          |     |            |              |            |            |            |

| QR10                         |     | 8.894e-03  | 7.1244e-03   | 2.449e-03  | 1.331e-02  | 2.750e-03  |

| QR11                         |     | 4.072e-04  | 2.8045e-04   | 2.166e-04  | 5.901e-04  | 2.178e-04  |

| QR12                         |     | -1.223e-06 | - 4.9053e-07 | -6.314e-07 | -6.917e-07 | -5.722e-07 |

| Reverse Bias Leakage Current |     |            |              |            |            |            |

| IR10                         |     | 9.452e+00  | 4.131e+00    | 9.443e+02  | 1.080e+03  | -5.312e+03 |

| IR11                         |     | -4.458e-02 | -1.024e-02   | -5.433e+00 | -6.624e+00 | 1.179e+01  |

| IR12                         |     | 5.279e-05  | 1.499e-05    | 7.720e-03  | 1.011e-02  | 1.899e-02  |

| IR20                         |     | -6.145e+01 | 3.139e+02    | 4.282e+02  | 8.983e+02  | 2.593e+03  |

| IR21                         |     | 5.100e+00  | 1.285e+00    | 5.984e-01  | 1.376e+00  | -9.529e+00 |

| IR22                         |     | -9.340e-03 | -2.328e-03   | -3.170e-03 | -2.876e-03 | 1.403e-02  |

| IR30                         |     | -1.070e+02 | -8.821e+00   | 9.213e+00  | 6.234e+00  | -2.737e+01 |

| IR31                         |     | 6.884e-01  | 1.222e-01    | 7.580e-02  | -2.149e-02 | 1.679e-01  |

| IR32                         |     | -9.643e-04 | -1.824e-04   | -2.087e-04 | 4.070e-05  | -2.159e-04 |

Figure 4: Measured and simulated static forward characteristics of the CSD04060 MPS SiC diode.

Figure 5: Measured and simulated static reverse characteristics of the CSD04060 MPS SiC diode.

Figure 6: Measured and simulated thermal impedance characteristics of the CSD04060 MPS SiC diode.

Figure 7: Measured and simulated reverse recovery charge characteristics of the CSD04060 MPS SiC diode.

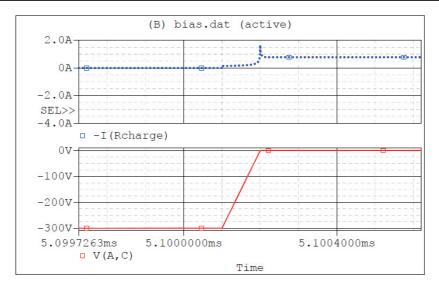

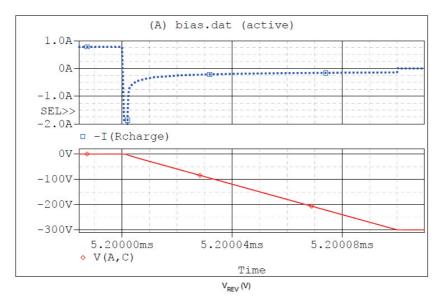

The SiC MPS diode's (CSD04060) simulation of the dynamic behavior shown in figures 8 and 9, exhibits that the elimination of the stored charge starts when the voltage becomes negative. However, the final verification of the dynamic model has yet to be carried out in a cell of a switching power converter.

Figure 8. Simulated dynamic behavior of the C3D04060 diode (turn-on).

Figure 9. Simulated dynamic behavior of the C3D04060 diode (turn-off).

## 4. Conclusion

The proposed SiC MPS diodes behavioral electrothermal model demonstrates excellent correspondence between the simulated forward and reverse bias and the curves provided by the devices' manufacturers. The estimation process of parameters which is based on two methods (i.e. weighted least square (WLS) and simulated annealing (SA)) has yielded satisfactory results. The basic advantage of the proposed model lies in its immanent simplicity and flexibility as to be implemented in modern simulators, adopting Spice programming (such as Berkeley SPICE, PSPICE.

#### References

- [1] B.J. Baliga, "Analysis of a High-Voltage Merged p-i-n/Schottky (MPS) Rectifier". *IEEE Electron Device Letters*, Vol. EDL-8, No. 9. September 1987.

- [2] H.J. Hua, L.H. Liang, Z.Y. Ming, Z.Y. Men, T.X. Yan, C.F. Ping, & S.Q. Wen "Simulation study of a mixed terminal structure for 4H-SiC merged PiN/Schottky diode" *Chin. Phys.* B Vol. 20, No. 11 (2011) 118401.

- [3] S. M. Sze, & Kwok K. Ng "Physics of Semiconductor Devices" 3rd Edition A John Wiley & Sons 2007

- [4] B. J Baliga "Fundamentals of power semiconductor devices" Springer Science 2008

- [5] J.S. Yuan & J.J. Liou "Semiconductor Device Physics and Simulation" *Plenum Press* 1998.

- [6] T.R. McNutt, A.R. Hefner Jr, H.A. Mantooth, J.L. Duliere, D.W. Berning, & R. Singh "Physics-based modeling and characterization for silicon carbide power diodes" *Science Direct, Solid-State Electronics* Volume 50, Issue 3, March 2006, Pages 388 398

- [7] J. Dąbrowski, & J. Zarębski "Silicon Power Schottky Diodes Model Implemented in SPICE" *TCSET* 2008, February 19-23, 2008, *Lviv-Slavsko*, Ukraine

- [8] F. N. Masana "SiC Schottky Diode Electrothermal Macromodel" MIXDES 2010, 17th *International Conference "Mixed Design of Integrated Circuits and Systems"*, June 24-26, 2010, Wroclaw, Poland.

- [9] K.J. Tseng, C.F. Foo & P.R. Palmer "Implementing power diode models in Spice and Saber" 0-7803-18S9-S/94/\$4.00 1994 *IEEE*.

- [10] G. L. Skibinski & W.A. Sethares "Thermal Parameter Estimation Using Recursive Identification" *IEEE Transactions on power electronics*. Vol 6. No 2, April 1991

- [11] K. V. V. Murthy & R. E. Bedford "Transformation Between Foster and Cauer Equivalent Networks" *IEEE Transactions on Circuits and Systems*, Vol. CAS -25, No. 4, April 1978

- [12] Star-Hspice Manual, Release 1998.2, July 1998

- [13] Cadence OrCad, Help Product version 16.6 October 2012

- [14] G. Massobrio, & P. Antognetti, Semiconductor Device Modeling with SPICE, 2nd edition, *McGraw Hill*, 1 December 1998.

- [15] J. Luo, K.J. Chung, H. Huang, & J.B. Bernstein, "Temperature dependence of Ron-sp in silicon carbide and GaAs Schottky diode" *IEEE* 02CH37320. 40th Annual international Reliability Physics Symposium, Dallas. Texas, 2002.

- [16] H. A Mantooth, Senior Member, IEEE, & Jeffrey L. Duliere "A Unified Diode Model for Circuit Simulation" *IEEE Transactions On Power Electronics*, Vol. 12, No. 5, September 1997.

- [17] A. Maxim, D. Andreu, & J. Boucher, «A Unified High Accuracy SPICE Library For The Power Semiconductor Devices Built With The Analog Behavioral Macromodeling Technique" ISPSO 2000. May 22-25. Toulouse, France.

- [18] Y.C Liang, & V.J Gosbell "Diode Forward and Reverse Recovery Model for Power Electronic SPICE Simulations" *IEEE Transactions on power electronics*. Vol 5. No 3. July 1990.

- [19] CSD04060-Silicon Carbide Schottky Diode, Datasheet, Rev. Q, Cree.

- [20] N. Jankovic, T. Ueta, K. Hamada, T. Nishijima, & P. Igic "Unified Approach in Electro-Thermal Modelling of IGBTs and Power PiN Diodes" *Proceedings of the 19th International Symposium on Power Semiconductor Devices & ICs* May 27-30, 2007 Jeju, Korea.

- [21] A. Guerra, & F. Vallone, "Electro-Thermal SPICE Schottky Diode Model Suitable Both at Room Temperature and at High Temperature," *International Rectifier*, Dec. 1999.

- [22] M. Marz, & P. Nance, "Thermal Modeling of Power Electronic Systems," Fraunhofer Institute, April. 2000.

- [23] F.N. Masana "A straightforward analytical method for extraction of semiconductor device transient thermal parameters" Microelectronics Reliability 47 (2007) 2122–2128 Science Direct Elsevier

- [24] R. Chibante "Simulated Annealing Theory with Applications" Published by *Sciyo* First published September 2010.

- [25] C3D04060E Silicon Carbide Schottky Diode, Datasheet, Rev. E, Cree.

- [26] CSD10030 -Silicon Carbide Schottky Diode, Datasheet, Rev. B, Cree.

- [27] SDP04S60 -Silicon Carbide Schottky Diode, Datasheet, Rev. 2.5, Infineon.

- [28] SDP10S30 -Silicon Carbide Schottky Diode, Datasheet, Rev. 1.5, Infineon.

The IISTE is a pioneer in the Open-Access hosting service and academic event management. The aim of the firm is Accelerating Global Knowledge Sharing.

More information about the firm can be found on the homepage: <a href="http://www.iiste.org">http://www.iiste.org</a>

## CALL FOR JOURNAL PAPERS

There are more than 30 peer-reviewed academic journals hosted under the hosting platform.

**Prospective authors of journals can find the submission instruction on the following page:** <a href="http://www.iiste.org/journals/">http://www.iiste.org/journals/</a> All the journals articles are available online to the readers all over the world without financial, legal, or technical barriers other than those inseparable from gaining access to the internet itself. Paper version of the journals is also available upon request of readers and authors.

#### MORE RESOURCES

Book publication information: <a href="http://www.iiste.org/book/">http://www.iiste.org/book/</a>

## **IISTE Knowledge Sharing Partners**

EBSCO, Index Copernicus, Ulrich's Periodicals Directory, JournalTOCS, PKP Open Archives Harvester, Bielefeld Academic Search Engine, Elektronische Zeitschriftenbibliothek EZB, Open J-Gate, OCLC WorldCat, Universe Digtial Library, NewJour, Google Scholar