# **Different SRAM Cells Using Low Power Reduction Techniques**

Manpreet Kaur<sup>1</sup>, Navdeep Kaur<sup>2</sup>, Amit Grover<sup>3\*</sup>, Neeti Grover<sup>4</sup>

- 1. Department of Electronics and Communication Engineering, Shaheed Bhagat Singh State Technical Campus, Moga Road (NH-95), Ferozepur-152004, India.

- 2. Department of Electronics and Communication Engineering, Shaheed Bhagat Singh State Technical Campus, Moga Road (NH-95), Ferozepur-152004, India.

- 3. Department of Electronics and Communication Engineering, Shaheed Bhagat Singh State Technical Campus, Moga Road (NH-95), Ferozepur-152004, India.

- 4. Department of Applied Sciences & Humanities, Shaheed Bhagat Singh State Technical Campus, Moga Road (NH-95), Ferozepur-152004, India.

\*Email of the corresponding author: <u>amitgrover 321@rediffmail.com</u>

#### **Abstract**

With increasing technology, usage of SRAM Cells has been increased to large extent while designing the system on-chips in CMOS technology. Power consumption and the speed are the major factors of concern for designing a chip along with the leakage power. The consumption of power and speed of SRAMs are some important issues among a number of factors that provides a solution which describes multiple designs that minimize the consumption of power and this article is also based on that. This article presents the simulation of 6T, 8T and 9T SRAM cells using low power reduction techniques and develops a modified model that provides the consumer with a product that costs less and having reduced power delay product. All the simulations have been carried out on 90nm at Tanner EDA tool. The entire circuit verification is done using the Tanner tool.

**Keywords:** CMOS Logic, SRAM and VLSI.

#### 1. Introduction

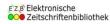

Figure 1 shows the write mode. Word line is used for enabling the access transistors M1 and M2 for write operation [13].

Figure.1 6T SRAM Conventional [1]

Memory Architecture is Random-access architecture which is an Asynchronous design. The SRAM IC is R/W memory circuit that permits the modification (writing) as well as their retrieval (reading). The SRAM IC was developed using the CDS IC446 [8], cadence IC design environment. The design was based on the AMI 0.6-micron process. The popular, full CMOS 6-transistor cell configuration was used to design the SRAM memory array [2]. Some of the advantages of using full CMOS SRAM configuration include high switching speeds [3].

In order to design a 64 bit SRAM, 64 full CMOS 6-T cells were used. Each full CMOS 6-T [9] cell has a capability of storing 1 bit [5]. Based on the literature survey, it has been concluded that SRAM [12] memory cell dissipate large amount of power [4] during rise time and fall time of input data because at that time the direct path exist between the  $V_{dd}$  and ground.

#### 2. Low Power SRAM

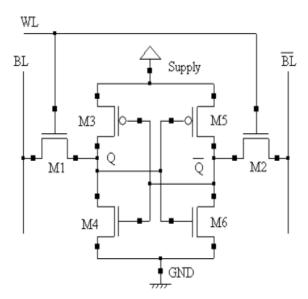

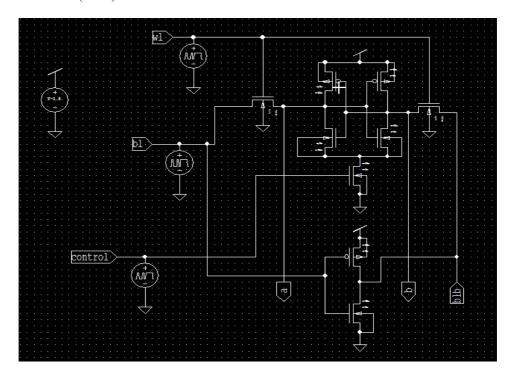

Figure 2 shows the write mode SRAM. SRAM [13] cell introduced one Control signal transistor for controlling these transistors in this figure. But due to one more transistors area is increased in comparison to Conventional approach. This control transistor uses control select signals which can properly control the dissipation [3] [10] in power.

Figure.2 6-T

Figure.3 8-T

Figure 3 shows the dual-port cell (8T-cell) created by adding two transistors; the read [11] can be entirely decoupled from the write operation in an 8T [1] cell by sensing the data through a separate read stack controlled by a separate read word lines (RWL).

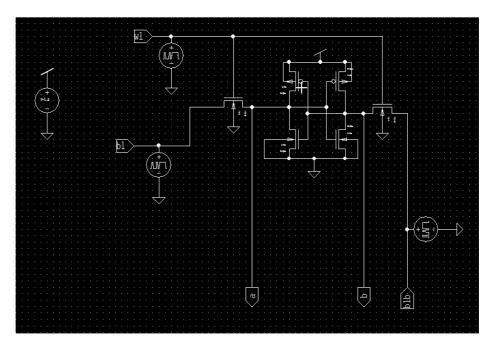

Figure.4 9-T

The schematic of the 9T SRAM cell, for CMOS technology, is shown in Figure 4. The upper sub circuit of the 9T [15] memory circuit is essentially a 6-T with minimum sized devices (composed of M3, M4, M5, M6, M1 and M2). Write signal (WL) control M5 and M6. The data is stored within this upper memory sub-circuit [7]. The lower sub circuit of the new cell is composed of the bit-line access transistors (M7 and M8) and the read access transistor (M9).

#### 3. Simulation Analysis

All the circuits have been simulated using 90 nm technology on Tanner EDA tool. To make the impartial testing environment all the circuits has been simulated on the same input patterns.

### 4. Simulation Results

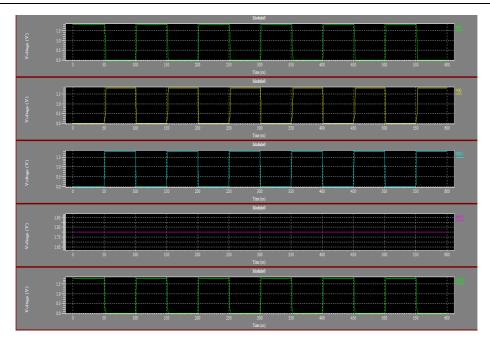

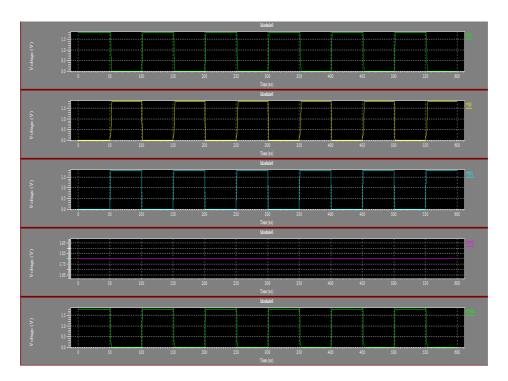

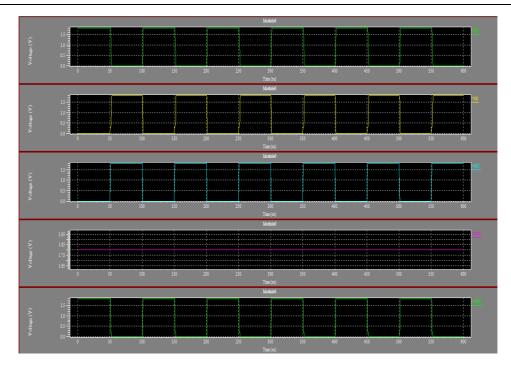

Figures 5 to 7 shows output waveforms of different SRAM cells at 90nm technology.

Figure.5 Output Waveform of 6T

Figure.6 Output Waveform of 8T

Figure.7 Output Waveform of 9T

#### 5. Final Results

The observations of power and delay of different SRAM cells are shown in table 1.

Table I. POWER AND DELAY COMPARISON OF DIFFERENT SRAM CELLS AT 90 NM TECHNOLOGIES

| Design<br>Style | No. of<br>transistors | Minimum<br>Length (μm) | Avg. Power<br>Consumption<br>(watts) | Prop. Delay (nsec)    |

|-----------------|-----------------------|------------------------|--------------------------------------|-----------------------|

| 6T              | 6                     | .09                    | 2.2x10 <sup>-4</sup>                 | 1.9x10 <sup>-10</sup> |

| 8T              | 8                     | .09                    | 3.2x10 <sup>-4</sup>                 | 2.6x10 <sup>-10</sup> |

| 9Т              | 9                     | .09                    | 1.9x10 <sup>-3</sup>                 | 1.2x10 <sup>-9</sup>  |

#### 6. Conclusions

The most efficient technique to reduce the power dissipation is the reduction of the supply voltage. The power dissipation reduction in SRAMs is not only due to power supply voltage reduction, but also due to operating frequency and temperature. Technology scaling demands a decrease in both  $V_{dd}$  and  $V_t$  to sustain delay reduction, while restraining active power dissipation. To increase their reliability, the lifetime of battery is a prime concerned at the cost of speed. Reduction in the power consumption reduces the problems associated with high temperature and also provides an additional benefit in terms of the extended life of the battery.

#### 7. References

- [1] Prashant Upadhyay and Mr. Rajesh Mehra, "Low Power Design of 64-bits Memory by using 8-T Proposed SRAM Cell", International Journal of Research and Reviews in Computer Science (IJRRCS), Vol. 1, No. 4, December 2010.

- [2] Sreerama Reddy G. M, P. Chandrashekara Reddy, "Design and VLSI Implementation of 8 Mb Low Power SRAM in 90nm", European Journal of Scientific Research, Vol.26 No.2, pp.305-314, 2009.

- [3] Keejong Kim, Hamid Mahmoodi, "A Low-Power SRAM Using Bit-Line Charge-Recycling", IEEE Journal of Solid-state Circuits, Vol. 43, No. 2, Feb 2008.

- [4] Yung-Do Yang and Lee-Sup Kim, "A Low-Power SRAM Using Hierarchical Bit Line and Local Sense Amplifiers" IEEE Journal of solid state circuits, Vol.40, No. 6, June 2005.

- [5] Chang, Y., Lai, F. and Yang, C., "Zero-aware asymmetric SRAM cell for reducing cache power in writing zero", IEEE Trans. VLSI Systems, Vol. 12, no. 8, pp. 827-36,2004.

- [6] Aly, R., Faisal, M. and Bayoumi, A., "Low-power cache design using 7T SRAM cell" in Proc. IEEE System on Chip Conference, pp. 171-174, 2005.

- [7] Varun Kumar Singhal, Balwinder Singh, "Comparative study of power reduction techniques for Static random access memory" International Journal of VLSI and Signal Processing Applications, Vol. 1, Issue 2, pp. 80-88, May 2011.

- [8] Irina Vazir, Prabhjot S. Balaggan, Sumandeep Kaur, Cailan Shen, "SRAM IP for DSP/SoC Projects" San Jose State University SRAM.

- [9] Ashish Siwach, Rahul Rishi," Asymmetric SRAM- Power Dissipation and Delay" IJCEM International Journal of Computational Engineering & Management, Vol. 11, pp. 28 31, January 2011.

- [10] Texas Instruments, "CMOS Power Consumption and Cpd Calculation" SCAA035B June 1997.

- [11] Debasis Mukherjee, Hemanta Kr. Mondal and B.V.R. Reddy, "Static Noise Margin Analysis of SRAM Cell for High Speed Application" IJCSI International Journal of Computer Science Issues, Vol. 7, Issue 5, pp. 175 180, September 2010.

- [12] Shilpi Birla, Neeraj Kr. Shukla, Manisha Pattanaik, R.K.Singh, Device and Circuit Design Challenges for Low Leakage SRAM for Ultra Low Power Applications" Canadian Journal on Electrical & Electronics Engineering Vol. 1, No. 7, December 2010.

- [13] Sapna Singh, Neha Arora, Neha Gupta, Meenakshi Suthat, "Simulation and Analysis of 6T SRAM Cell Using Power Reduction Techniques", IOSR Journal of Engineering, Vol. 2, Issue 1, pp. 145-149. Jan 2012.

- [14] Benton H. Calhoun, Member, IEEE, and Anantha P. Chandrakasan, Fellow, IEEE, "Static Noise Margin Variation for Sub-threshold SRAM in 65-nm CMOS" IEEE Journal of Solid-state Circuits, Vol. 41, No. 7, July 2006.

- [15] N.M. Sivamangai1 and K. Gunavathi2, Non-members, "A Low Power SRAM Cell with High Read Stability" ECTI Transactions on Electrical Engineering, Electronics and Communications Vol. 9, No. 1 February 2011.

- [16] Srinivasa Rao, Raghavendra Sirigiri, V. Malleswara Rao, "New Technique for Reducing Sub-threshold leakage in SRAM" International Journal of Engineering Sciences Research-IJESR may 2011.

- [17] Syed Shakib Sarwar, Syed an Nazmus saqueb, Farhan Quaiyum (student member, IEEE), and a. b. m. harun-ur rashid (Senior Member, IEEE), "Memristor-Based Nonvolatile Random Access Memory: Hybrid Architecture for Low Power Compact Memory Design", IEEE, Volume 1February 3, 2013,accepted April 14, 2013, published May 10, 2013.

#### **Biography**

**Manpreet kaur** has been pursuing her research work under the guidance of Ms. Navdeep kaur, Assistant Professor (ECE) and Mr. Amit Grover, Assistant Professor (ECE), Shaheed Bhagat Singh State Technical Campus, Ferozepur, Punjab, India. The author place of birth is Sultanpur Lodhi, Kapurthala, Punjab, India on 08<sup>th</sup> July 1990.

Navdeep Kaur has received her M. Tech degree in Communication Systems in 2008 from GNDU, Amritsar and her B. Tech degree in E&I in 2005 from AIET, Faridkot, affiliated to PTU, Kapurthala. She has been working in teaching from last four and half years. Currently, she is working as an Assistant Professor in Shaheed Bhagat Singh State Technical Campus, Ferozepur, Punjab, India. The author place of birth is Hoshiarpur, Punjab, India on 21<sup>st</sup> March 1984. Her area of interest includes neural networks, Wireless communications and VLSI Design.

Amit Grover (M'06-SM'09-PI'11&12) The author became a Member (M) of Association ISTE in 2006, a Senior Member (SM) of society SELCOME in september 2009, and a Project-Incharge (PI) in august 2011 and in September 2012. The author place of birth is Ferozepur, Punjab, India on 27<sup>th</sup>, September 1980. The author received M. Tech degree in Electronics and Communication Engineering from Punjab Technical University, Kapurthla, Punjab, India in 2008 and received his B. Tech degree in Electronics and Communication Engineering from Punjab Technical University, Kapurthala, Punjab, India in 2001. Currently, he is working as an Assistant Professor in Shaheed Bhagat Singh State Technical Campus (Established by Punjab Government), Moga road, Ferozpur, 152004, Punjab, India. The author is a Reviewer of many Reputed International Journals. His area of interest includes signal processing, MIMO systems, Wireless mobile communication; high speed digital communications, 4G Wireless Communications and VLSI Design.

Neeti Grover received her master degree in Applied Sciences from Guru Nanak Dev University, Amritsar, and Punjab, India in 2007 and received her Bachelor"s degree from Guru Nanak Dev University, Amritsar, Punjab, India in 2004. Her place of birth is Jallandhar, Punjab, India on 29th, December 1983. Currently, she is working as an Assistant Professor in the department of Applied Sciences and Humanities in Shaheed Bhagat Singh State Technical Campus, Ferozpur, Punjab, India.

The IISTE is a pioneer in the Open-Access hosting service and academic event management. The aim of the firm is Accelerating Global Knowledge Sharing.

More information about the firm can be found on the homepage: http://www.iiste.org

#### CALL FOR JOURNAL PAPERS

There are more than 30 peer-reviewed academic journals hosted under the hosting platform.

**Prospective authors of journals can find the submission instruction on the following page:** <a href="http://www.iiste.org/journals/">http://www.iiste.org/journals/</a> All the journals articles are available online to the readers all over the world without financial, legal, or technical barriers other than those inseparable from gaining access to the internet itself. Paper version of the journals is also available upon request of readers and authors.

#### MORE RESOURCES

Book publication information: <a href="http://www.iiste.org/book/">http://www.iiste.org/book/</a>

Recent conferences: <a href="http://www.iiste.org/conference/">http://www.iiste.org/conference/</a>

## **IISTE Knowledge Sharing Partners**

EBSCO, Index Copernicus, Ulrich's Periodicals Directory, JournalTOCS, PKP Open Archives Harvester, Bielefeld Academic Search Engine, Elektronische Zeitschriftenbibliothek EZB, Open J-Gate, OCLC WorldCat, Universe Digtial Library, NewJour, Google Scholar